芯片资讯

热点资讯

- FPGA排序-冒泡排序(Verilog版)介绍

- Infineon品牌SLE 4432 C芯片IC EEPROM 256BYTE CHIP的技术和方案应用介绍

- 深度解析索尼的多重曝光HDR技术

- FPGA浮点IP内核究竟有哪些优势呢?

- EEPROM的数据保持时间有多长?

- Microchip微芯半导体AT97SC3205T-X3A1C20B芯片FF COM I2C TPM 4.4MM TSS

- Melexis品牌MLX81113KDC-BAB-000-RE芯片IC LIN RGB CTRLR 32KB 4CH 8

- Melexis品牌MLX81150LLW-DAA-000-RE芯片IC LIN SLAVE 32K FLASH 32QF

- 聊一聊MEMS先生的微机电系统

- Melexis品牌MLX81150LLW-DAA-000-SP芯片IC LIN SLAVE 32K FLASH 32QF

- 发布日期:2024-01-02 12:34 点击次数:131

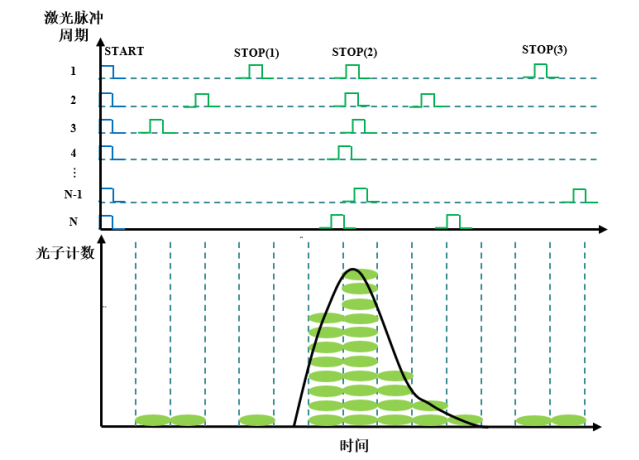

1 . TCSPC技术原理

TCSPC时间相关单光子计数技术是一种成熟且通用的单光子计数技术,是一种功能强大的分析方法,目前广泛应用于荧光寿命测量、时间分辨光谱、荧光寿命成像、飞行时间测量等众多领域,尤其是在生命科学和基础物理学中使用。

TCSPC技术使用高重复频率的脉冲激光器作为光源,使用高灵敏度探测器对信号多次重复测量,计量离散光子脉冲实现甄别信号,把探测器探测到的信号看成单个光子形成的脉冲序列,每当探测器输出一个脉冲则代表探测到一个光子,不是记录脉冲强度,而是记录脉冲密度来实现测量。

单光子探测器的输出信号是对应于探测到单个光子的随机分布的脉冲序列。一般情况下,一个信号周期内探测到多于一个光子的几率是很小的,有些信号周期会探测到一个光子,也有可能许多信号周期内没有检测到光子。

当探测到一个光子时,就可以在信号周期内测得与探测器脉冲对应的时间。每记录一次这样的事件(光子),就在对应的存储单元中加“1”,该存储单元的地址与探测时间对应。在记录了许多光子之后,就可以根据存储器中各个单元的光子数,得到探测时间的分布,即光脉冲的波形。

TCSPC技术将多个激光脉冲周期采集到的光子信号累积,光子信号与激光同步信号之间具有时间相关性,会在时域上形成光子计数峰,同时剔除随机分布在各个时刻,芯片交易网IC交易网计数值较少的暗计数。如图1所示为TCSPC计数原理。

图1 TCSPC计数原理

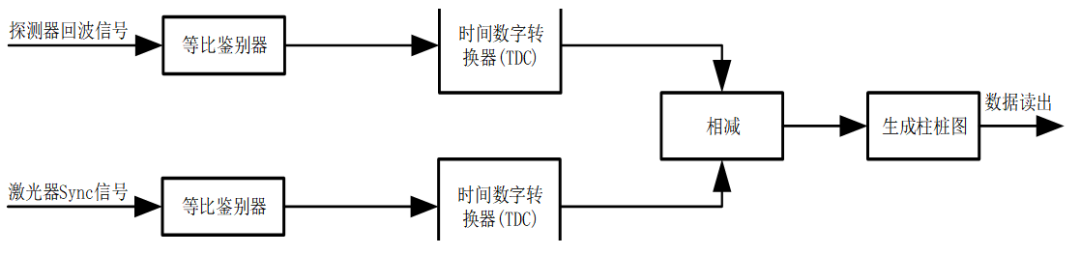

2 .TCSPC计数FPGA实现

在普通的激光测距系统中, EEPROM带电可擦可编程存储器芯片大全可以将经过TDC时间数字转换技术求取的时刻值通过传输接口, ATMEGA系列ATMEL芯片COM传输给上位机软件或直接由MCU进行处理, 电子元器件PDF资料大全得到测距值。但是在多通道、高重频单光子激光三维成像系统中, CMOS图像传感器集成电路芯片为了得到高质量的图像信息,势必需要大容量的点云数据,进行分析,此时,EEPROM带电可擦可编程存储器芯片大全需要进行实时的在线处理,完成图像数据的提取。

图2为时间相关单光子技术模块结构图,在这里,等比鉴别器我们将在后续的文章中做具体的讲解,而时间数字转换器的FPGA实现前面已分多个章节讲解过,在这里主要讲解,如何在FPGA中实现在线的TCSPC的累积,即生成柱状图。有需要的读者,可以联系笔者,下载程序,或者一起探讨。

图2 时间相关单光子技术模块

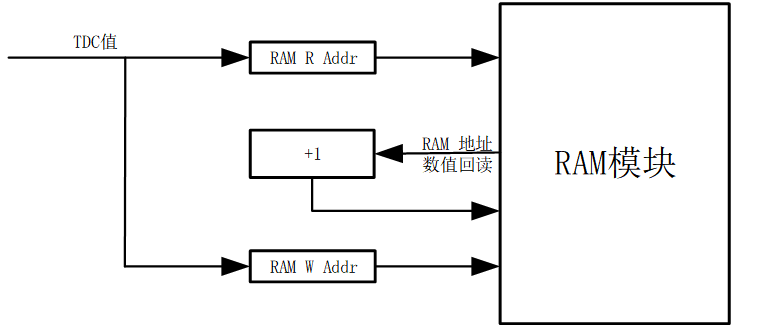

其实,FPGA实现TCSPC的累积相对比较简单,也就是统计时刻值的个数。通过FPGA内的RAM模块进行实现,如图3所示。

将计算得到的TDC值作为RAM的读写地址,首先将当前的时刻值的统计值从RAM中读出,然后完成加1,将新的计数值存在RAM中,这样完成一个TCSPC累积,根据系统具体的累积时间要求,完成TCSPC的累积。

图3时间相关光子计数FPGA实现

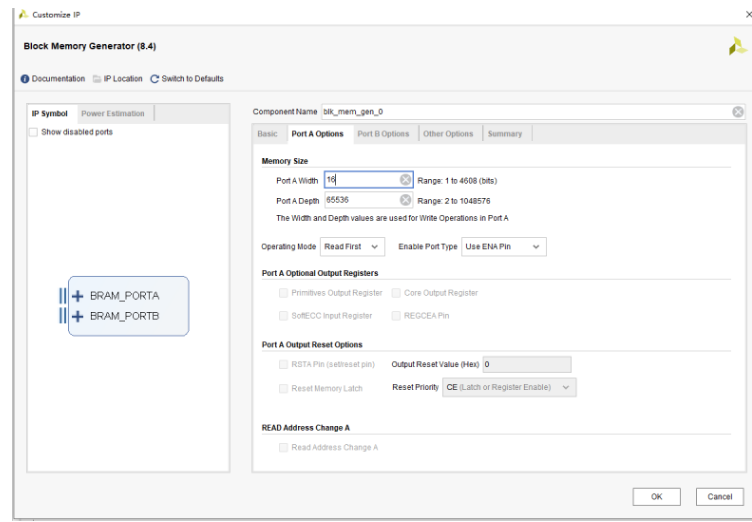

根据上次基于多相位的TDC设计,输出的TDC值位宽为16bit,因此在这里设置简单双端口RAM的界面如图4所示,数据位宽为16bit,即累积最大的值为65536,数据深度为65536(根据TDC的位宽决定)。

图4 RAM IP核设置

//* tb文件,从文件中读取仿真数据 //

reg [15:0]TDC_data[4999:0];

integer i;

initial

begin

i=0;

begin

$readmemh("D:/TDC_data.txt",TDC_data,0,4999);

end

forever

begin

@(posedge Clk_in or posedge Reset)

if(Reset == 1'b1)

begin

TDC_Data1

TDC_Data_Valid1

end

else

begin

i

TDC_Data1

TDC_Data_Valid1

end

end

end

// FPGA部分代码 //

ram_enb

ram_ena

ram_wea

ram_addra

ram_dina

if(acc_cnt == 16'd5000)//累积5000个数据结束

begin

ms_ram

acc_cnt

end

else

begin

fms_ram

acc_cnt

end

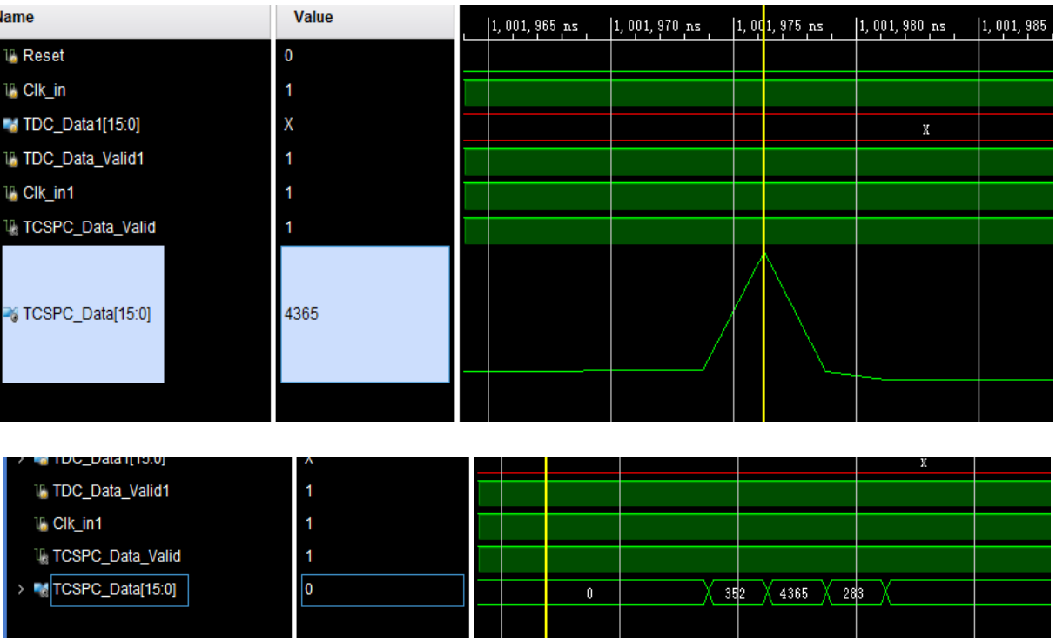

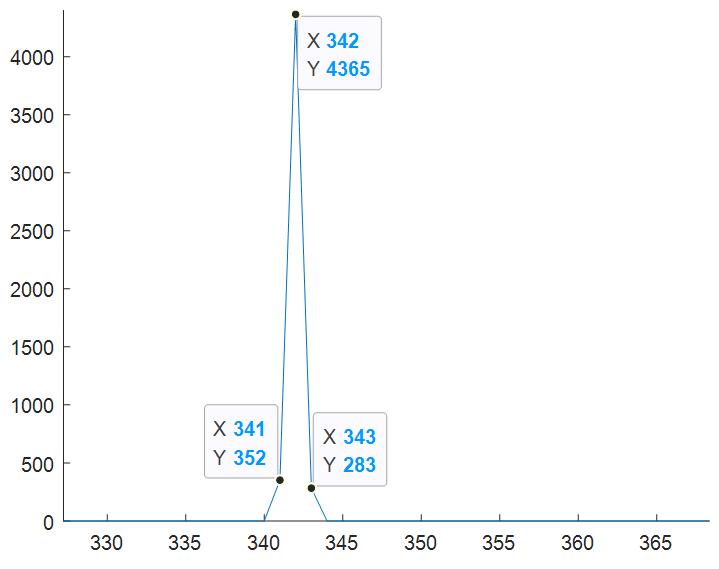

图5为TCSPC仿真结果图,在这里累积了5000个点,在实际程序中,可以按累积时间点来计算,也可以按数据点数来计算。和图6 Matlab程序进行比较,得出FPGA的计算结果是正确的。

图5 TCSPC FPGA仿真结果

图6为TCSPC Matlab计算结果图

- 基于微纳结构的MEMS热辐射红外光源技术原理2024-01-16

- 盛思锐推出基于紫外吸收测量原理的首款水质传感器SWT50i2024-01-05

- 基于FPGA的贪吃蛇小游戏实现案例2024-01-05

- 一种简单的、真实的基于循环序列的FIFO缓存设计2024-01-05

- 一种基于柔性超疏水碳纳米管纤维薄膜的高性能桥式气流传感器开发2024-01-04

- 等效时间采样原理及基于FPGA的实现2024-01-03