芯片资讯

热点资讯

- FPGA排序-冒泡排序(Verilog版)介绍

- Infineon品牌SLE 4432 C芯片IC EEPROM 256BYTE CHIP的技术和方案应用介绍

- 深度解析索尼的多重曝光HDR技术

- FPGA浮点IP内核究竟有哪些优势呢?

- EEPROM的数据保持时间有多长?

- Microchip微芯半导体AT97SC3205T-X3A1C20B芯片FF COM I2C TPM 4.4MM TSS

- Melexis品牌MLX81113KDC-BAB-000-RE芯片IC LIN RGB CTRLR 32KB 4CH 8

- Melexis品牌MLX81150LLW-DAA-000-RE芯片IC LIN SLAVE 32K FLASH 32QF

- 聊一聊MEMS先生的微机电系统

- Melexis品牌MLX81150LLW-DAA-000-SP芯片IC LIN SLAVE 32K FLASH 32QF

- 发布日期:2024-01-03 08:30 点击次数:77

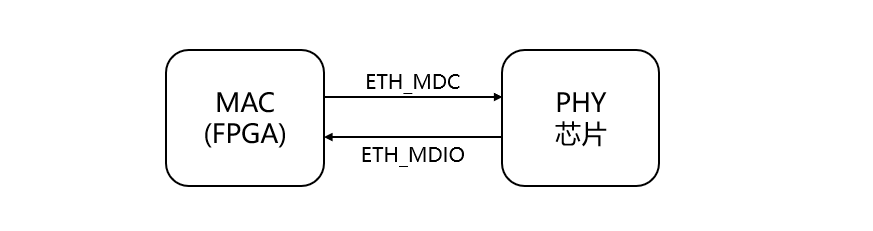

本文开源一个FPGA项目:MDIO接口读写测试。以太网通信模块主要由 MAC (Media Access Control)控制器和物理层接口 PHY (Physical Layer)两部分构成。其中,MAC控制器和PHY可以整合到同一芯片内,也可以分开,即MAC控制器由FPGA实现,PHY由以太网芯片实现。PHY芯片内部寄存器数据读写是通过MDIO接口实现的,可以对PHY芯片工作模式进行配置并获取PHY芯片工作状态。

01PHY芯片

PHY芯片发送数据时,将MAC控制器发来的数据转化为串行数据流,按照物理层编码规则把数字信号转化为模拟信号发出去,接收数据反之。

另外,PHY芯片具有自协商功能。当连接好网线时,PHY芯片会自动检测对端设备,并通过协商确定连接速度、双工模式等。最终确定两个设备同时支持的最大数据传输速度和最佳双工模式。

PHY地址

本文以YT8511 PHY芯片为例。其PHY地址由LED_ACT和RXD[1:0]决定。PHY地址一共有5位,高2位固定为0,LED_ACT和RXD[1:0]表示低3位,可以通过硬件电路进行配置。即地址范围从00001到00111。

复位

PHY芯片支持软硬件复位,硬件复位是通过将ETH_RST_N引脚拉低10ms实现,软件复位是通过向地址0x00寄存器的bit[15]写入1进行复位,复位完成后,该位会自动清零。

寄存器

YT8511共有22位寄存器,常用的就只有控制寄存器、基本状态寄存器、和PHY芯片特定状态寄存器:

控制寄存器用于控制芯片复位、内部回环模式、选择网速、自协商等功能;

基本状态寄存器用于获取PHY芯片自协商状态、连接状态;

PHY芯片特定状态寄存器用于获取PHY芯片连接速度。

02MDIO接口

MAC和PHY芯片之间有一个配置接口,FPGA通过MDIO接口对PHY芯片内部寄存器进行配置,一般来讲PHY芯片在默认寄存器配置下就可以正常工作。

MDIO接口也被成为SMI接口,即串行管理接口。具体包括时钟(ETH_MDC)和数据输入输出(ETH_MDIO)信号接口。其中,时钟信号频率应低于12.5Mhz。

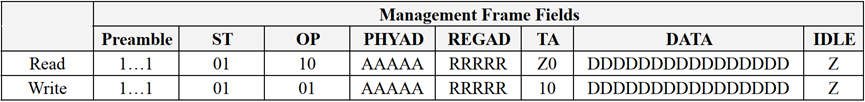

通信协议

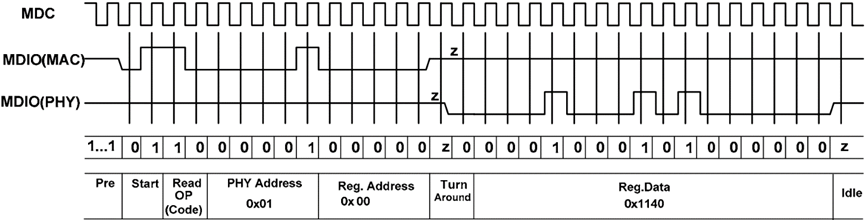

MDIO接口通信协议如上图所示, 电子元器件PDF资料大全其中:

Preamble :32位前导码, CMOS图像传感器集成电路芯片用于同步PHY芯片;

ST :2位帧开始信号;

OP :2位操作码,芯片交易网IC交易网读10, EEPROM带电可擦可编程存储器芯片大全写01;

PHYAD :5位PHY地址, ATMEGA系列ATMEL芯片COM用于确定与那个PHY芯片进行通信;

REGAD :5位寄存器地址;

TA (Turnaround):2位转向。在读命令中,MDIO在此时由MAC驱动改为PHY驱动,在第1位,MDIO引脚为高阻状态,第2位,PHY将MDIO引脚拉低,准备发送数据;在写命令中,EEPROM带电可擦可编程存储器芯片大全不需要MDIO方向发生变化,MAC固定输出10,随后开始写入数据;

DATA :16位数据;

IDLE :空闲状态,此时MDIO为无源驱动,处于高阻状态,但一般用上拉电阻使其上拉至高电平。

读时序

MDIO接口读时序如上图所示,以读取0x00地址下寄存器数据为例。整个读操作过程的MDC时钟由MAC驱动,同时MAC驱动MDIO引脚输出前导码+帧开始+操作码+PHY地址+寄存器地址,随后MDIO引脚切换至PHY驱动。在第一个TA位,MDIO引脚为高阻状态,第二个TA位为低电平,表示PHY芯片成功响应,并且接下来会输出16位寄存器数据;而如果第二个TA位处于高电平,则PHY芯片响应失败,有可能PHY地址不正确或者其它时序的错误。

需要注意的是,PHY在MDC时钟的上升沿采集数据,为保证数据的稳定传输,MAC在MDC的下降沿更新MDIO引脚的数据。当MDIO引脚切换至PHY驱动时,MDIO数据在MDC时钟的下降沿更新,因此MAC在MDC时钟的上升沿采集数据。在读操作结束后,MAC将MDIO引脚输出高阻,此时MDIO引脚的外部上拉电阻会将MDIO引脚拉高,此时MDIO接口处于空闲状态。

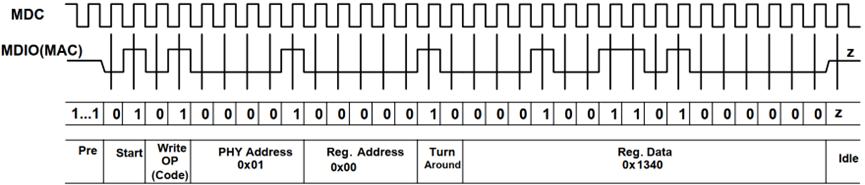

写时序

MDIO接口写时序如上图所示,以往0x00地址下寄存器写入0x1340为例。在整个写操作过程中,MDC时钟和MDIO引脚一直由MAC端驱动,按照MDIO接口写通信协议开始传输数据。需要注意的是,PHY在MDC时钟的上升沿采集数据,为保证数据的稳定传输,MAC在MDC的下降沿将数据更新至MDIO引脚。在写操作结束后,MAC将MDIO引脚输出高阻,此时MDIO引脚的外部上拉电阻会将MDIO引脚拉高,此时MDIO接口处于空闲状态。

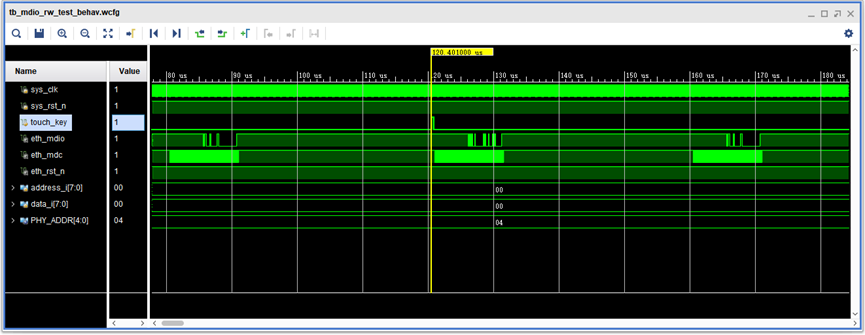

03实现功能

本文开源的MDIO读写模块实现的功能主要是:FPGA通过MDIO接口每隔一定时间循环读取PHY芯片各个寄存器的值,并通过MDIO接口对PHY芯片进行软复位。其中,mdio_dri实现了MDIO接口数据读写驱动,mdio_ctrl实现了MDIO读写控制功能。使用Vivado软件仿真结果如下图所示:

- 全球FPGA芯片市场布局2025-10-08

- Microchip微芯半导体AT17LV002A-10CU芯片IC FPGA EEPROM 2M ALTERA 8LAP的技术和方案应用介绍2025-10-06

- Microchip微芯半导体AT17LV002-10TQU芯片IC FPGA EEPROM 2M 10MHZ 44TQFP的技术和方案应用介绍2025-10-05

- Microchip微芯半导体AT17N512-10SI芯片IC FPGA 512K CONFIG MEM 20SOIC的技术和方案应用介绍2025-10-04

- Microchip微芯半导体AT17N512-10SC芯片IC FPGA 512K CONFIG MEM 20SOIC的技术和方案应用介绍2025-09-29

- Microchip微芯半导体AT17N512-10PI芯片IC FPGA 512K CONFIG MEM 8DIP的技术和方案应用介绍2025-09-28