芯片资讯

热点资讯

- FPGA排序-冒泡排序(Verilog版)介绍

- Infineon品牌SLE 4432 C芯片IC EEPROM 256BYTE CHIP的技术和方案应用介绍

- 深度解析索尼的多重曝光HDR技术

- FPGA浮点IP内核究竟有哪些优势呢?

- EEPROM的数据保持时间有多长?

- Microchip微芯半导体AT97SC3205T-X3A1C20B芯片FF COM I2C TPM 4.4MM TSS

- Melexis品牌MLX81113KDC-BAB-000-RE芯片IC LIN RGB CTRLR 32KB 4CH 8

- Melexis品牌MLX81150LLW-DAA-000-RE芯片IC LIN SLAVE 32K FLASH 32QF

- 聊一聊MEMS先生的微机电系统

- Melexis品牌MLX81150LLW-DAA-000-SP芯片IC LIN SLAVE 32K FLASH 32QF

你的位置:EEPROM带电可擦可编程IC存储器芯片大全-亿配芯城 > 芯片资讯 > 介绍一种IP控制信号的处理方式

介绍一种IP控制信号的处理方式

- 发布日期:2024-01-03 12:41 点击次数:192

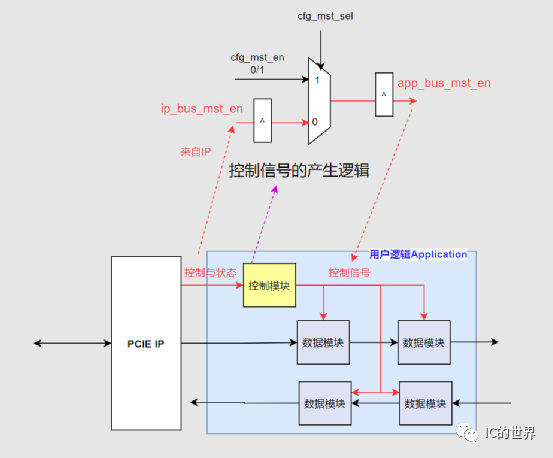

在ASIC/FPGA项目中,我们会用到很多IP,其中有很多IP存在内部控制信号以及内部状态信号。这些控制信号和内部状态信号影响数据流的接收和发送。

以PCIe为例,蓝色框图部分为PCIe用户侧逻辑,是需要用户实现的逻辑。

左侧白色为PCIe IP,PCIe内部配置空间有一个控制信号,名为bus_master_en(简写),当bus_master_en为0时,芯片交易网IC交易网不期望用户逻辑发送dma请求(memory读写请求)。

所以在用户逻辑中,

EEPROM带电可擦可编程存储器芯片大全我们就需要感知到这些信号的数值,

ATMEGA系列ATMEL芯片COM用于控制数据逻辑模块。 通常我们期望这些信号是可控的,

电子元器件PDF资料大全能够灵活配置,

CMOS图像传感器集成电路芯片EEPROM带电可擦可编程存储器芯片大全既给芯片加了一层保障,又方便debug。

即使对IP或者协议的理解有误,也能通过配置规避大部分问题。

那一种很常见的方式就是,添加一个mux,默认情况下,使用ip驱动的控制信号。

如图所示:

ip_bus_mst_en是ip输出的控制信号。

app_bus_mst_en用于控制内部数据模块。

cfg_mst_en和cfg_mst_sel都来自配置csr模块,可灵活配置成0或者1.

cfg_mst_sel默认值为0,表示选择ip_bus_mst_en,在默认情况下,app_bus_mst_en的数据与ip_bus_mst_en相同

通常我们期望这些信号是可控的,

电子元器件PDF资料大全能够灵活配置,

CMOS图像传感器集成电路芯片EEPROM带电可擦可编程存储器芯片大全既给芯片加了一层保障,又方便debug。

即使对IP或者协议的理解有误,也能通过配置规避大部分问题。

那一种很常见的方式就是,添加一个mux,默认情况下,使用ip驱动的控制信号。

如图所示:

ip_bus_mst_en是ip输出的控制信号。

app_bus_mst_en用于控制内部数据模块。

cfg_mst_en和cfg_mst_sel都来自配置csr模块,可灵活配置成0或者1.

cfg_mst_sel默认值为0,表示选择ip_bus_mst_en,在默认情况下,app_bus_mst_en的数据与ip_bus_mst_en相同

这种设计小技巧在IC项目中比较普遍,但是又时常被忘记。 审核编辑:刘清

相关资讯

- Microchip微芯半导体PIC16F18144T-I/6N芯片7KB FLASH, 512B RAM, 128B EEPROM的技术和方案应用介绍2025-11-11

- Microchip微芯半导体PIC16F18124T-I/7N芯片7KB FLASH, 512B RAM, 128B EEPROM的技术和方案应用介绍2025-11-10

- Microchip微芯半导体PIC16F18114T-I/MD芯片7KB FLASH, 512B RAM, 128B EEPROM的技术和方案应用介绍2025-11-09

- Microchip微芯半导体PIC18F16Q20-I/P芯片64KB FLASH, 4K RAM, 256 EEPROM,的技术和方案应用介绍2025-11-08

- Microchip微芯半导体PIC18F56Q43T-I/6LX芯片64KB FLASH, 4KB RAM, 1KB EEPROM,的技术和方案应用介绍2025-11-07

- Microchip微芯半导体PIC18F46Q43T-I/PT芯片64KB FLASH, 4KB RAM, 1KB EEPROM,的技术和方案应用介绍2025-11-06