芯片资讯

热点资讯

- FPGA排序-冒泡排序(Verilog版)介绍

- Infineon品牌SLE 4432 C芯片IC EEPROM 256BYTE CHIP的技术和方案应用介绍

- 深度解析索尼的多重曝光HDR技术

- FPGA浮点IP内核究竟有哪些优势呢?

- EEPROM的数据保持时间有多长?

- Microchip微芯半导体AT97SC3205T-X3A1C20B芯片FF COM I2C TPM 4.4MM TSS

- Melexis品牌MLX81113KDC-BAB-000-RE芯片IC LIN RGB CTRLR 32KB 4CH 8

- Melexis品牌MLX81150LLW-DAA-000-RE芯片IC LIN SLAVE 32K FLASH 32QF

- 聊一聊MEMS先生的微机电系统

- 大疆的低成本高阶智能驾驶方案详解

- 发布日期:2024-01-05 08:03 点击次数:126

很多芯片在设计之初,就已经考虑如何增加代码的复用性,尽量减少工作量,降低错误概率。 增加复用性的几个场景:

不同项目之间的代码复用性

不同工艺之间的代码复用性

同一个模块例化多份,分别工作在不同模式下

同一个项目不同环境(RTL验证,FPGA demo 验证)之间的代码复用性

本章节将简单谈谈几种增加代码复用性的方法。

1、基础模块IP化

在各家ASIC/FPGA项目的代码目录中,我们经常能看到各类小的基础模块,例如各类跨时钟模块、各类调度仲裁模块、各类RAM读写模块、各类总线接口模块等等。它们可能命名为share_ip_*或base_ip_*或cmn_ip_*,又或者其他名称,几乎每个设计者都需要用到这些基础模块。 我们在需要实现其相关功能时,只需要例化模块即可,简单高效,有降低了bug概率。

2、模块参数化

在进行模块设计时,我们需要尽量保证模块参数化,尽量避免使用立即数(例如10’d0)。 被参数化的信号可能是数据位宽,芯片交易网IC交易网用户数量或者其他类型的信号。

module ip_bus_sync #( //

parameter DATA_WDTH = 16 ,

EEPROM带电可擦可编程存储器芯片大全 //

parameter INI_VALUE = {DATA_WDTH{1'b0}} //

)(

input i_src_clk ,

ATMEGA系列ATMEL芯片COM //

input i_src_rst_n ,

电子元器件PDF资料大全 //

input [DATA_WDTH-1:0] i_src_din ,

CMOS图像传感器集成电路芯片 //

input i_dst_clk , //

input i_dst_rst_n , //

output reg [DATA_WDTH-1:0] o_dst_dout //

);

//逻辑代码

endmodule

3、宏定义区分代码分支

ASIC项目的代码一般至少有两个版本:ASIC版本和验证版本(FPGA/加速器)。部分公司还会同时出两个系列的芯片,ASIC系列和FPGA系列。因此我们通常需要通过宏定义区分不同的代码分支和参数

`ifdef FOR_ASIC_DESIGN //ASIC logic //参数定义 `else //其他分支逻辑 //参数定义 `endif

`ifdef FOR_ASIC_DESIGN generate genvar i; for ( i=0; i

4、使用参数选择代码分支

在同一个宏定义分支下(例如同在ASIC或者FPGA项目),EEPROM带电可擦可编程存储器芯片大全我们可能需要奖模块例化多份,以支持如下场景:

Case1:同一个模块,工作在同的模式下,为了节约资源,只需要保留对应模式的代码逻辑。 Case2:同一个模块,其支持的功能数量不同,所需要的RAM等资源也不相同,需要例化不同规格的RAM。

module xxxxx

#(

parameter FUNCTION_MODE = `MULTI_FUNCTION

)

(

//各类IO信号

) ;

generate

if (FUNCTION_MODE==`MULTI_FUNCTION) begin:MULTI_FUNCTION_CODE

//多function 逻辑

end

else begin:SINGLE_FUNCTION_CODE

// 单function 逻辑

end

end

endgenerate

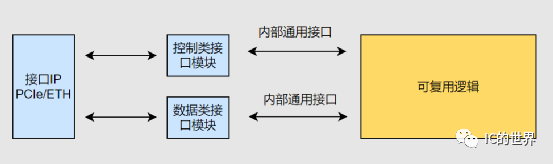

5、IP接口隔离

不同Vendor的IP的用户侧接口大概率是不一样的,为了避免因为IP替换导致的大量代码修改,可以在设计之处就考虑将IP接口隔离。例如通过2类接口转换模块(控制类和数据类),将所需要的控制信号和数据流信号转换成通用的内部信号,这样无论怎么替换IP,都只需要修改少量代码。

6、std cell 隔离

我们通常会将std cell外包一层或者多层代码,这样就能将工艺与设计代码尽量分离。

常见的有bit同步器,ram,clk-gating,clk mux等模块。如下是单bit同步器的案例。

module ip_bit_sync #( parameter DATA_WDTH = 1 // bit width)(in put wire i_dst_clk, // destination clockinput wire [(DATA_WDTH-1):0] i_src_din, // data inputoutput wire [(DATA_WDTH-1):0] o_dst_dout // data output);`ifdef FOR_ASIC_DESIGNgenerategenvar i;for ( i=0; i

审核编辑:刘清

- Microchip微芯半导体PIC16F18174T-I/MP芯片7KB FLASH, 512B RAM, 128B EEPROM的技术和方案应用介绍2025-12-12

- 盛思锐(Sensirion)传感器芯片全系列供应2025-12-12

- Microchip微芯半导体PIC16F17156T-I/SO芯片28KB FLASH, 2KB RAM, 128B EEPROM的技术和方案应用介绍2025-12-11

- GigaDevice (兆易创新) 芯片系列全解2025-12-11

- Microchip微芯半导体PIC16F17175T-I/PT芯片14KB FLASH, 1KB RAM, 128B EEPROM的技术和方案应用介绍2025-12-10

- Microchip微芯半导体PIC16F18174T-I/PT芯片7KB FLASH, 512B RAM, 128B EEPROM的技术和方案应用介绍2025-12-08